IoTGateway/Features/Linux/Display

Contents

- 1 Single Channel LVDS Panel

- 2 Dual Channel LVDS Panel

- 3 Touchscreen Panel

- 4 MIPI DSI Panel

- 5 HOWTOs

- 5.1 How to set display in u-boot command

- 5.2 How to fix display resolution

- 5.3 How to get the current display mode

- 5.4 How to get the supported display modes

- 5.5 How to get the monitor's EDID

- 5.6 How to control the screen blanking

- 5.7 How to customize u-boot logo

- 5.7.1 Yocto 2.1

- 5.7.1.1 You need to modify u-boot files as below:

- 5.7.1.2 You can refer to Setting_up_SDK to setup environment for building u-boot image

- 5.7.1.3 After you patch file, you need to build u-boot image(Example:ROM-3420 DDR 1G)

- 5.7.1.4 Generate u-boot logo image

- 5.7.1.5 Upload u-boot image and u-boot log image to eMMC by mgtool

- 5.7.2 LTIB

- 5.7.3 Android

- 5.7.1 Yocto 2.1

- 5.8 How to customize Android logo

- 5.9 How to modify dts file for setting different framebuffer

- 5.10 How to bring up panel in Yocto 2.5 and later

- 6 ThreeDisplayImx8

- 7 Limitation

- 8 New Panel in 2021

- 9 Panel in iMX8

Single Channel LVDS Panel

96LEDK-C070WV50NA1

- The following operations are performed with RSB-4210 and BSP version 20120705 (i.MX5).

- u-boot

- get u-boot-2009.08_V1.1.patch and use it to patch by the following commands:

$ cd ${BSP_20120705_BASE}/source/u-boot-2009.08/

$ patch -p1 < ../u-boot-2009.08_V1.1.patch

- include/asm-arm/clock.h

- add one new enumerated

PIXEL_CLK

- add one new enumerated

enum {

CPU_CLK = 0,

PERIPH_CLK,

AHB_CLK,

IPG_CLK,

IPG_PERCLK,

UART_CLK,

CSPI_CLK,

DDR_CLK,

NFC_CLK,

ALL_CLK,

PIXEL_CLK,

};

- cpu/arm_cortexa8/mx53/generic.c

- add one new case of the

switch (clk_type)in theint clk_config(...)

- add one new case of the

case PIXEL_CLK:

if (config_pixel_clk(ref, freq))

return -1;

break;

-

- add the follow lines at the end of the file

int config_pixel_clk(u32 ref, u32 freq)

{

int ret = 0;

u32 pll = 0;

struct pll_param pll_param;

memset(&pll_param, 0, sizeof(struct pll_param));

pll = freq;

ret = calc_pll_params(ref, pll, &pll_param);

if (ret != 0) {

printf("Can't find pll parameters: %d\n",

ret);

return ret;

}

return config_pll_clk(PLL4_CLK, &pll_param);

}

- board/freescale/mx53_smd/mx53_smd.c

- insert the follow lines between

#ifdef CONFIG_ADV_SOM_CMX53and#else

- insert the follow lines between

static struct fb_videomode lvds_g070y2 = {

"G070Y2", 60, 800, 480, 33602, 100, 90, 10, 8, 2, 2,

FB_SYNC_EXT,

FB_VMODE_NONINTERLACED,

0,

};

-

- replace the part of the

... ipuv3_fb_init ... clk_config ...by the following:

- replace the part of the

ret = ipuv3_fb_init(&lvds_g070y2, di, IPU_PIX_FMT_RGB24,

DI_PCLK_LDB, 30000000);

clk_config(CONFIG_REF_CLK_FREQ, 30*7, PIXEL_CLK);

- u-boot environment variable

- set

bootargs_baseas below:

| setenv bootargs_base 'setenv bootargs console=ttymxc0,115200 ldb=single,di=1,ch0_map=JEIDA,ch1_map=JEIDA video=mxcdi0fb:RGB24,G070Y2 di1_primary,bpp=24' |

- linux kernel

- arch/arm/mach-mx5/mx53_smd.c

- insert the following lines into

static struct struct fb_videomode ldb_modefb[](or modify the existed "G070Y2") :

- insert the following lines into

{

"G070Y2", 60, 800, 480, 33602, 100, 90, 10, 8, 2, 2,

0,

FB_VMODE_NONINTERLACED, 0,

},

IDK-1115R-40XGC1E

- u-boot environment variable

- set

bootargs_baseas below:

| setenv bootargs_base 'setenv bootargs console=ttymxc0,115200 enable_wait_mode=off video=mxcfb0:dev=ldb,1024x768M@60,if=RGB24 ldb=sin0' |

AM-640480GETNQW-TA0H

Android 4.4.2 (Kernel 3.0.35)

- Timing

The clock frequency should be 25.175MHz. Need to modify the clock source form PLL2 (pll2_pfd_352M) to PLL5. (In arch/arm/mach-mx6/clock.c )

Ref: https://cache.freescale.com/files/32bit/doc/app_note/AN4509.pdf

Ref: https://community.nxp.com/thread/306801

android/kernel_imx/arch/arm/mach-mx6/clock.c b/new/arch/arm/mach-mx6/clock.c

(1) static struct clk ldb_di0_clk .parent = &pll2_pfd_352M, ==> .parent = &pll5_video_main_clk,

(2) static struct clk ldb_di1_clk .parent = &pll2_pfd_352M, ==> .parent = &pll5_video_main_clk,

(3) int __init mx6_clocks_init clk_set_parent(&ldb_di0_clk, &pll2_pfd_352M); --> clk_set_parent(&ldb_di0_clk, &pll5_video_main_clk);

clk_set_parent(&ldb_di1_clk, &pll2_pfd_352M); --> clk_set_parent(&ldb_di1_clk, &pll5_video_main_clk);

android/kernel_imx/drivers/video/mxc/ldb.c

static struct fb_videomode ldb_modedb[] = {

{

"LDB-VGA", 25, 640, 480, 39682,

160, 80,

45, 22,

5, 1,

FB_SYNC_HOR_HIGH_ACT | FB_SYNC_VERT_HIGH_ACT,

FB_VMODE_NONINTERLACED,

FB_MODE_IS_VESA},

- u-boot environment variable

- set

bootargsas below:

|

setenv bootargs console=ttymxc0,115200 androidboot.console=ttymxc0 vmalloc=400M init=/init video_mode=extension video=mxcfb0:dev=ldb,LDB-VGA,if=RGB666,bpp=32 video=mxcfb1:off video=mxcfb2:off video=mxcfb3:off fbmem=28M,28M androidboot.hardware=freescale pcie_testmode=off |

Dual Channel LVDS Panel

Calculating Timings parameter of LVDS Panel SOP OS: Yocto 1.8 Modify imx6qdl-advantech.dtsi Step1: In ldb parameter, add parameter --> split-mode; /* dual-channel setting *

&ldb {

ext_ref = "true";

status = "okay";

split-mode; /* dual-channel setting */

Step2: In lvds-channel@1, change [crtc = "ipu1-di1";] to [crtc = "ipu1-di0";]

lvds-channel@1 {

fsl,data-mapping = "spwg";

fsl,data-width = <24>;

/* crtc = "ipu1-di1"; */

crtc = "ipu1-di0"; /* dual-channel setting */

status = "okay";

Step3: In display-timings native-mode = <&timing0>, Delete the other panel parameter.Add" LTI370LN01 " Parameter

//Dual channel panel

timing0: lti370ln01 {

clock-frequency = <148500000>;

hactive = <1920>;

vactive = <544>;

hback-porch = <70>;

hfront-porch = <70>;

vback-porch = <200>;

vfront-porch = <200>;

hsync-len = <140>;

vsync-len = <185>;

};

Calculating Timings parameter Check your panel Timing table Example : samsung 37 inch panel

(1)clock-frequency --> Clock (MHz)

(2)hactive --> Horizontal Active Display Period

(3)vactive --> Vertical Active Display Period

(4)hback-porch + hfront-porch + hsync-len (Total) = Blanking = Horizontal Total - Horizontal Active Display Period

(5)vback-porch + vfront-porch + vsync-len (Total) = Blanking = Vertical Total - Vertical Active Display Period

U-boot command ( Must be add "video=mxcfb1:off")

setenv mmcargs setenv bootargs console=${console},${baudrate} ${smp} root=${mmcroot} video=mxcfb0:dev=ldb,1920x540M@60,if=RGB24 video=mxcfb1:off

Touchscreen Panel

E21D03U-C01-04 Irtouch-Dualtouch

IRTOUCH panel [Android 4.4]

(1) Download IRTOUCH driver (Irtouch-dualtouch-package-android-v14.2.0.0002.7z) (2) Download IRTOUCH SWAP mode tool (Swapmode.7z) (3) Swap mode You need to check and swap IRTOUCH 0X80. Please install SWAP mode tool in win7. Run SwapModeTool.exe and choose IRTOUCH 0X80. (4) Installing the IRTOUCH Dual-touch Touchscreen Driver (a) irtouchusb-dt.c locate to kernel_imx/driver/input/touchscreen; (b) modify Makefile in kernel_imx/driver/input/touchscreen add: "obj-$(CONFIG_TOUCHSCREEN_USBIRTOUCH_DT) += irtouchusb-dt.o" (c) modify Kconfig in kernel_imx/driver/input/touchscreen add: config TOUCHSCREEN_USBIRTOUCH_DT tristate "IRTOUCH USB Touchscreen Driver For single point" depends on USB_ARCH_HAS_HCD select USB help Say Y here if you have a IRTOUCH based touchscreen controller. If unsure, say N. To compile this driver as a module, choose M here: the module will be called irtouch. (d) You can make menuconfig select TOUCHSCREEN_USBIRTOUCH_DT and build kernel Modify defconfig CONFIG_TOUCHSCREEN_USBIRTOUCH_DT=y example : imx6_rsb4410_android_kk44_defconfig (e) Add one line to Android file system's ueventd.rc: File path : device/fsl/imx6/etc/ueventd.freescale.rc /dev/irtouch 0666 root root (f) Copy "Vendor_6615_Product_0081.idc" and "Vendor_6615_Product_0080.idc" file to the Android file system's /usr/idc directory. (5) Calibration the Touchscreen Install CalibrationTools.apk and run "CalibrationTools" to start calibrate touchscreen. package name:com.irtouch.android.calibration class name: CalibrationToolsActivity

eGTouch touch panel [Android 4.2 ~ Android 4.4]

(1) Add "eGalaxCalibrator" PRODUCK PACKAGES in device/fsl/imx6/iMX6.mk

(2) Add eGtouch file path in device/fsl/imx6/iMX6.mk

device/fsl/common/input/eGTouch_v2.5.2320.A/eGalaxTouch_VirtualDevice.idc:system/usr/idc/eGalaxTouch_VirtualDevice.idc \

device/fsl/common/input/eGTouch_v2.5.2320.A/eGTouchA.ini:data/eGTouchA.ini \

device/fsl/common/input/eGTouch_v2.5.2320.A/eGTouchD:system/bin/eGTouchD \

(3) Add eGtouch idc and ini file in device/fsl/imx6/BoardConfigCommon.mK

BOARD_USERDATAIMAGE_PARTITION_SIZE := 128M

device/fsl/common/input/eGTouch_v2.5.2320.A/eGTouchA.ini

device/fsl/common/input/eGTouch_v2.5.2320.A/eGTouchD

device/fsl/common/input/eGTouch_v2.5.2320.A/eGalaxTouch_VirtualDevice.idc

(4) Add service about eGTouch in device/fsl/rsb_4410/init.rc

service eGTouchD /system/bin/eGTouchD

class main

user root

group root

oneshot [Android 4.2 and 4.4 MP version is include eGTouch function]

IDK-1105R-50VGA1E

- The following operations are performed using Linux BSP 4410LBV2080.

- u-boot

- apparently specify LDB-VGA in video item contained in the variable

bootargs_base setenv bootargs_base 'setenv bootargs console=ttymxc0,115200 enable_wait_mode=off video=mxcfb0:dev=ldb,LDB-VGA,if=RGB666'

- linux kernel

- in drivers/video/mxc/ldb.c, insert the following lines into

static struct struct fb_videomode ldb_modefb[](or modify the existed "LDB-VGA") :

{

"LDB-VGA", 60, 640, 480, 39722,

50, 80,

24, 18,

30, 10,

0,

FB_VMODE_NONINTERLACED,

FB_MODE_IS_DETAILED,},

The following operations are performed using Android BSP imx6ABV3040_2016-06-21 (Android 4.4)

- Timing

The clock frequency should be 25.175MHz. Need to modify the clock source form PLL2 (pll2_pfd_352M) to PLL5. (In arch/arm/mach-mx6/clock.c )

[1] [2]http://advdownload.advantech.com/productfile/Downloadfile1/1-Q18T9C/IDK-1105_USER_MANUAL_ED.1_FINAL.PDF

- u-boot

setenv bootargs console=ttymxc0,115200 androidboot.console=ttymxc0 vmalloc=400M init=/init video_mode=display3 video=mxcfb0:dev=ldb,LDB-VGA,if=RGB666 video=mxcfb1:off fbmem=28M,10M androidboot.hardware=freescale pcie_testmode=off

- Android kernel

android/kernel_imx/arch/arm/mach-mx6/clock.c b/new/arch/arm/mach-mx6/clock.c

(1) static struct clk ldb_di0_clk .parent = &pll2_pfd_352M, ==> .parent = &pll5_video_main_clk,

(2) static struct clk gpu2d_core_clk .parent = &pll2_pfd_352M, ==> .parent = &pll5_video_main_clk,

(3) if (cpu_is_mx6q())

clk_set_parent(&gpu2d_core_clk[0], &pll3_usb_otg_main_clk);

clk_set_parent(&ldb_di0_clk, &pll2_pfd_352M); --> clk_set_parent(&ldb_di0_clk, &pll5_video_main_clk);

clk_set_parent(&ldb_di1_clk, &pll2_pfd_352M); --> clk_set_parent(&ldb_di1_clk, &pll5_video_main_clk);

android/kernel_imx/drivers/video/mxc/ldb.c

static struct fb_videomode ldb_modedb[] = {

{

"LDB-VGA", 60, 640, 480, 39722,

50, 80,

24, 15,

15, 5,

0,

FB_VMODE_NONINTERLACED,

FB_MODE_IS_DETAILED,},

IDK-1107WR-40WVA1E

Linux

The following operations are performed with RSB-4410(4410LBV2080 and eGTouch_v2.5.3810.L-ma.zip)

- u-boot

- specify the variable bootargs_base as below:

setenv bootargs_base 'setenv bootargs console=ttymxc0,115200 enable_wait_mode=off video_mode=extension video=mxcfb0:dev=ldb,800x480M@60,if=RGB666,bpp=32 ldb=sin0'

- linux kernel source

- linux kernel config

- selection

-

- Device Drivers --->

- Input device support --->

- <*> Event interface

- Miscellaneous devices --->

- <*> User level driver support

- HID Devices --->

- [*] /dev/hidraw raw HID device support

- Special HID drivers --->

- <*> HID Multitouch panels

- Input device support --->

- Device Drivers --->

- deselection

-

- Device Drivers --->

- Input device support --->

- [*] Touchscreens --->

- < > USB Touchscreen Driver

- [*] Touchscreens --->

- Input device support --->

- Device Drivers --->

- root filesystem

- update

- /etc/rc.d/rc.local

Android

The following operations are performed with RSB-4410(4410ABV1080 and eGTouch_v2.5.2320.A-all.zip)

- u-boot

- specify the variable bootargs_base as below:

| setenv bootargs 'console=ttymxc0,115200 androidboot.console=ttymxc0 vmalloc=400M init=/init video=mxcfb0:dev=ldb,800x480M@60,if=RGB666,bpp=32 video=mxcfb1:off video=mxcfb2:off video=mxcfb3:off fbmem=28M androidboot.hardware=freescale' |

- linux kernel config

|

Device Drivers --->

|

- copy and rename

.configtoarch/arm/configs/imx6_rsb4410_android_defconfig

- root filesystem contained in BSP

- eGalaxCalibrator

IDK-1107WP-50WV-A1E

For Yocto 1.8 and later

- Display setting

- u-boot

u-boot bootargs need to be set as below:

setenv mmcargs setenv bootargs console=${console},${baudrate} ${smp} root=${mmcroot} video=mxcfb0:dev=ldb,800x480M@60,if=RGB24 video=mxcfb1:off video=mxcfb2:off;

- kernel

Need to change clock source, so we modify dts file.

imx6q-rom3420-a1.dts is taken as an example:

Add the code as below to dts file

&clks {

fsl,ldb-di0-parent = <&clks IMX6QDL_CLK_PLL5_VIDEO_DIV>;

fsl,ldb-di1-parent = <&clks IMX6QDL_CLK_PLL5_VIDEO_DIV>;

};

If produst is i.MX6QP , we have to modify arch/arm/mach-imx/clk-imx6q.c as below

(It's just a workaround solution)

//if (cpu_is_imx6q() && imx_get_soc_revision() == IMX_CHIP_REVISION_2_0) {

// clk[IMX6QDL_CLK_LDB_DI0_SEL] = imx_clk_mux_flags("ldb_di0_sel", base + 0x2c, 9, 3, ldb_di_sels, ARRAY_SIZE(ldb_di_sels), CLK_SET_RATE_PARENT);

// clk[IMX6QDL_CLK_LDB_DI1_SEL] = imx_clk_mux_flags("ldb_di1_sel", base + 0x2c, 12, 3, ldb_di_sels, ARRAY_SIZE(ldb_di_sels), CLK_SET_RATE_PARENT);

//} else {

/*

* The LDB_DI0/1_SEL muxes are registered read-only due to a hardware

* bug. Set the muxes to the requested values before registering the

* ldb_di_sel clocks.

*/

disable_anatop_clocks();

init_ldb_clks(np);

clk[IMX6QDL_CLK_LDB_DI0_SEL] = imx_clk_mux_ldb("ldb_di0_sel", base + 0x2c, 9, 3, ldb_di_sels, ARRAY_SIZE(ldb_di_sels));

clk[IMX6QDL_CLK_LDB_DI1_SEL] = imx_clk_mux_ldb("ldb_di1_sel", base + 0x2c, 12, 3, ldb_di_sels, ARRAY_SIZE(ldb_di_sels));

//}

- Touch setting

- kernel config setting

You could check this by make menuconfig

Necessary

Device Drivers --->

Input device support --->

<*> Event interface

Miscellaneous devices --->

<*> User level driver support

HID support --->

[*] /dev/hidraw raw HID device support

Special HID drivers --->

<*> HID Multitouch panels

Remove

Device Drivers --->

Input device support --->

[*] Touchscreens --->

< > USB Touchscreen Driver

- Note

- eGTouch_v2.5.7413.L-ma /eGTouchARMhf/eGTouchARMhfnonX or eGTouchARMhfwithX

- 1. Need to copy “eGTouchL.ini” into Linux system directory “/etc/eGTouchL.ini” and copy eGTouchD under /usr/bin..

- 2. Add "/usr/bin/eGTouchD " in /etc/rc.local

- Touch calibration on Yocto

- Step 1

- Step 2

- Step 3

MIPI DSI Panel

AUO G101UAN02

Enable auo in deconfig

bitbake linux-imx -c menuconfig

Enable option:

Device Drivers -> Graphics support -> Display Panels -> support for AUO G101UAN02 panel

Re-generated image

bitbake -c compile -f linux-imx bitbake -c deploy -f linux-imx bitbake fsl-image-qt5-validation-imx

Flash image

cd ~/imx8_5720/build-xwayland/tmp/deploy/images/imx8mqrom5720a1 bzcat ./fsl-image-qt5-validation-imx-imx8mqrom5720a1-XXXX.rootfs.sdcard.bz2 | sudo dd of=/dev/sdX bs=1M

Change dts in u-boot parameter. (Please type enter while the system is in count down process during boot to bootloader.)

setenv fdt_file adv-imx8mq-rom5720-a1-dcss-auog101uan02.dtb saveenv boot

HOWTOs

How to set display in u-boot command

Set HDMI in u-boot command mode is taken as an example:

| # setenv mmcargs setenv bootargs console=${console},${baudrate} ${smp} root=${mmcroot} video=mxcfb0:dev=hdmi,1920x1080M@60,if=RGB24 video=mxcfb1:off video=mxcfb2:off;boot |

Set LVDS in u-boot command mode is taken as an example:

| # setenv mmcargs setenv bootargs console=${console},${baudrate} ${smp} root=${mmcroot} video=mxcfb0:dev=ldb,800x480M@60,if=RGB24 video=mxcfb1:off video=mxcfb2:off;boot |

Set VGA in u-boot command mode is taken as an example:

| # setenv mmcargs setenv bootargs console=${console},${baudrate} ${smp} root=${mmcroot} video=mxcfb0:dev=lcd,1920x1080M@60,if=RGB24 video=mxcfb1:off video=mxcfb2:off;boot |

How to fix display resolution

Set resolution in u-boot command mode Set HDMI 640x480 and VGA 1920x1080 is taken as an example:

| # setenv mmcargs setenv bootargs console=${console},${baudrate} ${smp} root=${mmcroot} video=mxcfb0:dev=hdmi,640x480M@60,if=RGB24 video=mxcfb1:dev=lcd,1920x1080M@60,if=RGB24 video=mxcfb2:off;boot |

Set HDMI 1920x1080 and VGA 640x480 is taken as an example:

| # setenv mmcargs setenv bootargs console=${console},${baudrate} ${smp} root=${mmcroot} video=mxcfb0:dev=hdmi,1920x1080M@60,if=RGB24 video=mxcfb1:dev=lcd,640x480M@60,if=RGB24 video=mxcfb2:off;boot |

How to get the current display mode

# cat /sys/class/graphics/fb0/mode U:1920x1080p-60

How to get the supported display modes

# cat /sys/class/graphics/fb0/modes U:1280x720p-120 U:1280x720p-100 U:1920x1080p-30 U:1920x1080p-25 U:1920x1080p-24 U:1920x1080p-50 U:1440x576p-50 U:1440x576p-50 U:1440x288p-50 U:1440x288p-50 U:1280x720p-50 U:720x576p-50 U:720x576p-50 U:1920x1080p-60 U:1440x480p-60 U:1440x480p-60 U:1440x240p-60 U:1440x240p-60 U:1280x720p-60 U:720x480p-60 U:720x480p-60 U:640x480p-60

How to get the monitor's EDID

# i2cdump -f -y -r 0x00-0x7F 2 0x50

No size specified (using byte-data access)

0 1 2 3 4 5 6 7 8 9 a b c d e f 0123456789abcdef

00: 00 ff ff ff ff ff ff 00 5a 63 28 0e 01 01 01 01 ........Zc(?????

10: 22 16 01 03 08 30 1b 78 2e e6 75 a4 56 4f 9e 27 "????0?x.?u?VO?'

20: 0f 50 54 bf ef 80 b3 00 a9 40 95 00 81 80 81 40 ?PT????.?@?.???@

30: 81 0f 81 00 71 4f 02 3a 80 18 71 38 2d 40 58 2c ???.qO?:??q8-@X,

40: 45 00 dd 0c 11 00 00 1e 00 00 00 ff 00 53 44 44 E.???..?.....SDD

50: 31 32 33 34 41 31 33 37 36 0a 00 00 00 fd 00 32 1234A1376?...?.2

60: 4b 18 52 11 00 0a 20 20 20 20 20 20 00 00 00 fc K?R?.? ...?

70: 00 56 41 32 32 34 38 20 53 45 52 49 45 53 00 34 .VA2248 SERIES.4

</syntaxhighlight></div>

How to control the screen blanking

to blank the primary display

# echo 1 > /sys/class/graphics/fb0/blank

to unblank the primary display

# echo 0 > /sys/class/graphics/fb0/blank

to set auto-blanking timeout seconds

The default linux framebuffer support will blank a console after 600 seconds of no activity.

- kernel space

- specify kernel parameter 'consoleblank=<n>' (where <n> means timeout seconds) in u-boot's parameter, bootargs_base

- user space

- use the command,

setterm

- use the command,

How to customize u-boot logo

- About the following description, we use IDK-1107WR-40WVA1E panel to customize u-boot logo

- We customize u-boot logo for Yocto 2.1, LTIB and Android

Yocto 2.1

You need to modify u-boot files as below:

- 1. Modify the red string part in the uboot-imx6/arch/arm/imx-common/video.c file

@@ -52,6 +52,9 @@ int board_video_skip(void)

displays[i].mode.name,

displays[i].mode.xres,

displays[i].mode.yres);

#ifdef CONFIG_ADV_UBOOT_LOGO_DEBUG

printf("xxx\n");

#endif

} else

printf("LCD %s cannot be configured: %d\n",

displays[i].mode.name, ret);

- 2. Modify the red string part in the uboot-imx6/board/freescale/mx6advantech/mx6advantech.c file

@@ -744,18 +744,42 @@ static void enable_lvds(struct display_info_t const *dev)

struct iomuxc *iomux = (struct iomuxc *)

IOMUXC_BASE_ADDR;

u32 reg = readl(&iomux->gpr[2]);

#ifdef CONFIG_ADV_UBOOT_LOGO

reg |= IOMUXC_GPR2_DATA_WIDTH_CH0_24BIT |

IOMUXC_GPR2_DATA_WIDTH_CH1_24BIT;

#else

reg |= IOMUXC_GPR2_DATA_WIDTH_CH0_18BIT |

IOMUXC_GPR2_DATA_WIDTH_CH1_18BIT;

#endif

writel(reg, &iomux->gpr[2]);

}

struct display_info_t const displays[] = {{

.bus = -1,

.addr = 0,

#ifdef CONFIG_ADV_UBOOT_LOGO

.pixfmt = IPU_PIX_FMT_RGB24,

#else

.pixfmt = IPU_PIX_FMT_RGB666,

#endif

.detect = NULL,

.enable = enable_lvds,

.mode = {

#ifdef CONFIG_ADV_UBOOT_LOGO

.name = "Hannstar-XGA",

.refresh = 60,

.xres = 800,

.yres = 480,

.pixclock = 15385,

.left_margin = 220,

.right_margin = 40,

.upper_margin = 21,

.lower_margin = 7,

.hsync_len = 60,

.vsync_len = 10,

.sync = FB_SYNC_EXT,

.vmode = FB_VMODE_NONINTERLACED

#else

.name = "Hannstar-XGA",

.refresh = 60,

.xres = 1024,

@@ -769,6 +793,7 @@ struct display_info_t const displays[] = {{

.vsync_len = 10,

.sync = FB_SYNC_EXT,

.vmode = FB_VMODE_NONINTERLACED

#endif

} }, {

.bus = -1,

.addr = 0,

@@ -814,6 +839,10 @@ size_t display_count = ARRAY_SIZE(displays);

static void setup_display(void)

{

#ifdef CONFIG_ADV_UBOOT_LOGO_DEBUG

printf("ADV UBOOT LOGO setup display !!!\n");

#endif

struct mxc_ccm_reg *mxc_ccm = (struct mxc_ccm_reg *)CCM_BASE_ADDR;

struct iomuxc *iomux = (struct iomuxc *)IOMUXC_BASE_ADDR;

int reg;

@@ -825,11 +854,17 @@ static void setup_display(void)

imx_setup_hdmi();

/* Turn on LDB0, LDB1, IPU,IPU DI0 clocks */

#ifdef CONFIG_ADV_UBOOT_LOGO

/* mxc_ccm->CCGR3 address: 0x20c4074 */

#endif

reg = readl(&mxc_ccm->CCGR3);

reg |= MXC_CCM_CCGR3_LDB_DI0_MASK | MXC_CCM_CCGR3_LDB_DI1_MASK;

writel(reg, &mxc_ccm->CCGR3);

/* set LDB0, LDB1 clk select to 011/011 */

#ifdef CONFIG_ADV_UBOOT_LOGO

/* mxc_ccm->cs2cdr address: 0x20c402c */

#endif

reg = readl(&mxc_ccm->cs2cdr);

reg &= ~(MXC_CCM_CS2CDR_LDB_DI0_CLK_SEL_MASK

| MXC_CCM_CS2CDR_LDB_DI1_CLK_SEL_MASK);

@@ -837,34 +872,65 @@ static void setup_display(void)

| (3 << MXC_CCM_CS2CDR_LDB_DI1_CLK_SEL_OFFSET);

writel(reg, &mxc_ccm->cs2cdr);

#ifdef CONFIG_ADV_UBOOT_LOGO

/* mxc_ccm->cscmr2 address: 0x20c4020 */

#endif

reg = readl(&mxc_ccm->cscmr2);

reg |= MXC_CCM_CSCMR2_LDB_DI0_IPU_DIV | MXC_CCM_CSCMR2_LDB_DI1_IPU_DIV;

writel(reg, &mxc_ccm->cscmr2);

#ifdef CONFIG_ADV_UBOOT_LOGO

/* mxc_ccm->chsccdr address: 0x20c4034 */

#endif

reg = readl(&mxc_ccm->chsccdr);

reg |= (CHSCCDR_CLK_SEL_LDB_DI0

<< MXC_CCM_CHSCCDR_IPU1_DI0_CLK_SEL_OFFSET);

#ifdef CONFIG_ADV_UBOOT_LOGO

reg &= ~(MXC_CCM_CHSCCDR_IPU1_DI1_CLK_SEL_MASK);

#endif

reg |= (CHSCCDR_CLK_SEL_LDB_DI0

<< MXC_CCM_CHSCCDR_IPU1_DI1_CLK_SEL_OFFSET);

writel(reg, &mxc_ccm->chsccdr);

#ifdef CONFIG_ADV_UBOOT_LOGO

/* iomux->gpr[2] address: 0x20e0008 */

#endif

reg = IOMUXC_GPR2_BGREF_RRMODE_EXTERNAL_RES

| IOMUXC_GPR2_DI1_VS_POLARITY_ACTIVE_LOW

| IOMUXC_GPR2_DI0_VS_POLARITY_ACTIVE_LOW

| IOMUXC_GPR2_BIT_MAPPING_CH1_SPWG

#ifdef CONFIG_ADV_UBOOT_LOGO

| IOMUXC_GPR2_DATA_WIDTH_CH1_24BIT

#else

| IOMUXC_GPR2_DATA_WIDTH_CH1_18BIT

#endif

| IOMUXC_GPR2_BIT_MAPPING_CH0_SPWG

#ifdef CONFIG_ADV_UBOOT_LOGO

| IOMUXC_GPR2_DATA_WIDTH_CH0_24BIT

| IOMUXC_GPR2_LVDS_CH0_MODE_ENABLED_DI0

| IOMUXC_GPR2_LVDS_CH1_MODE_DISABLED;

#else

| IOMUXC_GPR2_DATA_WIDTH_CH0_18BIT

| IOMUXC_GPR2_LVDS_CH0_MODE_DISABLED

| IOMUXC_GPR2_LVDS_CH1_MODE_ENABLED_DI0;

#endif

writel(reg, &iomux->gpr[2]);

#ifdef CONFIG_ADV_UBOOT_LOGO

/* iomux->gpr[3] address: 0x20e000c */

#endif

reg = readl(&iomux->gpr[3]);

#ifdef CONFIG_ADV_UBOOT_LOGO

reg &= ~(IOMUXC_GPR3_LVDS1_MUX_CTL_MASK);

writel(reg, &iomux->gpr[3]);

#else

reg = (reg & ~(IOMUXC_GPR3_LVDS1_MUX_CTL_MASK

| IOMUXC_GPR3_HDMI_MUX_CTL_MASK))

| (IOMUXC_GPR3_MUX_SRC_IPU1_DI0

<< IOMUXC_GPR3_LVDS1_MUX_CTL_OFFSET);

writel(reg, &iomux->gpr[3]);

#endif

}

#endif /* CONFIG_VIDEO_IPUV3 */

@@ -985,9 +1051,15 @@ int board_early_init_f(void)

#if defined (CONFIG_ADVANTECH) && defined(CONFIG_SUPPORT_LVDS)

void setup_lvds_init(void)

{

#ifdef CONFIG_ADV_UBOOT_LOGO

imx_iomux_v3_setup_pad(IOMUX_LCD_BKLT_PWM | MUX_PAD_CTRL(NO_PAD_CTRL)); /* LCD_BKLT_PWM */

imx_iomux_v3_setup_pad(IOMUX_LCD_BKLT_EN | MUX_PAD_CTRL(NO_PAD_CTRL)); /* LCD_BKLT_EN */

imx_iomux_v3_setup_pad(IOMUX_LCD_VDD_EN | MUX_PAD_CTRL(NO_PAD_CTRL)); /* LCD_VDD_EN */

#else

imx_iomux_v3_setup_pad(IOMUX_LCD_BKLT_PWM); /* LCD_BKLT_PWM */

imx_iomux_v3_setup_pad(IOMUX_LCD_BKLT_EN); /* LCD_BKLT_EN */

imx_iomux_v3_setup_pad(IOMUX_LCD_VDD_EN); /* LCD_VDD_EN */

#endif

/* LCD_BKLT_PWM - disable pwm */

gpio_direction_output(LCD_BKLT_PWM, 0);

@@ -1005,15 +1077,44 @@ void setup_lvds_init(void)

#else

gpio_direction_output(LCD_VDD_EN, 0);

#endif

#ifdef CONFIG_ADV_UBOOT_LOGO_DEBUG

printf("ADV UBOOT LOGO setup_lvds_init \n");

#endif

}

#ifdef CONFIG_ADV_UBOOT_LOGO

void setup_lvds_poweron(void)

{

//LCD_BKLT_EN

gpio_direction_output(LCD_BKLT_EN, 1);

gpio_set_value(LCD_BKLT_EN,1);

//LCD_VDD_EN

gpio_direction_output(LCD_VDD_EN, 1);

gpio_set_value(LCD_VDD_EN,1);

gpio_direction_output(LCD_BKLT_PWM, 1);

gpio_set_value(LCD_BKLT_PWM,1);

}

#endif // #ifdef CONFIG_ADV_UBOOT_LOGO

#endif

int board_init(void)

{

#ifdef CONFIG_ADV_UBOOT_LOGO

printf("ADV UBOOT LOGO board_init() \n");

#endif

/* address of boot parameters */

gd->bd->bi_boot_params = PHYS_SDRAM + 0x100;

#if defined (CONFIG_ADVANTECH) && defined(CONFIG_SUPPORT_LVDS)

setup_lvds_init();

#ifdef CONFIG_ADV_UBOOT_LOGO

setup_lvds_poweron();

#endif

#endif

#ifdef CONFIG_MXC_SPI

setup_spi();

- 3. Modify the red string part in the uboot-imx6/drivers/video/cfb_console.c file

@@ -311,6 +311,19 @@ extern void video_get_info_str(int line_number, char *info); DECLARE_GLOBAL_DATA_PTR; #ifdef CONFIG_ADV_UBOOT_LOGO_EMMC #include <mmc.h> #include <common.h> #include <asm/ioNew.h> #define UBOOT_LOGO_BMP_ADDR 0x00100000 #define DISPLAY_WIDTH 800 #define DISPLAY_HEIGHT 480 #define DISPLAY_BPP 16 //#define CONFIG_FB_BASE (CONFIG_SYS_TEXT_BASE + 0x300000) #define CONFIG_FB_BASE VIDEO_FB_ADRS #endif /* Locals */ static GraphicDevice *pGD; /* Pointer to Graphic array */ @@ -1953,7 +1966,9 @@ static void *video_logo(void) } #endif /* CONFIG_SPLASH_SCREEN */ #ifndef CONFIG_ADV_UBOOT_LOGO_EMMC logo_plot(video_fb_address, video_logo_xpos, video_logo_ypos); #endif #ifdef CONFIG_SPLASH_SCREEN_ALIGN /* @@ -2090,6 +2105,14 @@ void video_clear(void) #endif } #ifdef CONFIG_ADV_UBOOT_LOGO_EMMC int get_mmc_env_devno(void) { uint soc_sbmr = readl(SRC_BASE_ADDR + 0x4); return (soc_sbmr & 0x00001800) >> 11; } #endif static int video_init(void) { unsigned char color8; @@ -2108,6 +2131,9 @@ static int video_init(void) /* Init drawing pats */ switch (VIDEO_DATA_FORMAT) { case GDF__8BIT_INDEX: #ifdef CONFIG_ADV_UBOOT_LOGO_DEBUG printf("Video: GDF__8BIT_INDEX ...\n"); #endif video_set_lut(0x01, CONSOLE_FG_COL, CONSOLE_FG_COL, CONSOLE_FG_COL); video_set_lut(0x00, CONSOLE_BG_COL, CONSOLE_BG_COL, @@ -2116,6 +2142,9 @@ static int video_init(void) bgx = 0x00000000; break; case GDF__8BIT_332RGB: #ifdef CONFIG_ADV_UBOOT_LOGO_DEBUG printf("Video: GDF__8BIT_332RGB ...\n"); #endif color8 = ((CONSOLE_FG_COL & 0xe0) | ((CONSOLE_FG_COL >> 3) & 0x1c) | CONSOLE_FG_COL >> 6); @@ -2128,6 +2157,9 @@ static int video_init(void) color8; break; case GDF_15BIT_555RGB: #ifdef CONFIG_ADV_UBOOT_LOGO_DEBUG printf("Video: GDF_15BIT_555RGB ...\n"); #endif fgx = (((CONSOLE_FG_COL >> 3) << 26) | ((CONSOLE_FG_COL >> 3) << 21) | ((CONSOLE_FG_COL >> 3) << 16) | @@ -2142,6 +2174,9 @@ static int video_init(void) (CONSOLE_BG_COL >> 3)); break; case GDF_16BIT_565RGB: #ifdef CONFIG_ADV_UBOOT_LOGO_DEBUG printf("Video: GDF_16BIT_565RGB ...\n"); #endif fgx = (((CONSOLE_FG_COL >> 3) << 27) | ((CONSOLE_FG_COL >> 2) << 21) | ((CONSOLE_FG_COL >> 3) << 16) | @@ -2156,6 +2191,9 @@ static int video_init(void) (CONSOLE_BG_COL >> 3)); break; case GDF_32BIT_X888RGB: #ifdef CONFIG_ADV_UBOOT_LOGO_DEBUG printf("Video: GDF_32BIT_X888RGB ...\n"); #endif fgx = (CONSOLE_FG_COL << 16) | (CONSOLE_FG_COL << 8) | CONSOLE_FG_COL; @@ -2164,6 +2202,9 @@ static int video_init(void) CONSOLE_BG_COL; break; case GDF_24BIT_888RGB: #ifdef CONFIG_ADV_UBOOT_LOGO_DEBUG printf("Video: GDF_24BIT_888RGB ...\n"); #endif fgx = (CONSOLE_FG_COL << 24) | (CONSOLE_FG_COL << 16) | (CONSOLE_FG_COL << 8) | @@ -2182,6 +2223,87 @@ static int video_init(void) /* Plot the logo and get start point of console */ debug("Video: Drawing the logo ...\n"); video_console_address = video_logo(); #ifdef CONFIG_ADV_UBOOT_LOGO_EMMC unsigned int size = DISPLAY_WIDTH * DISPLAY_HEIGHT * (DISPLAY_BPP / 8); unsigned char * pData; unsigned int start, count; int i, bmpReady = 0; int mmc_dev = get_mmc_env_devno(); #ifdef CONFIG_ADV_UBOOT_LOGO_DEBUG printf("mmc_dev:%d\n", mmc_dev); #endif struct mmc *mmc = find_mmc_device(mmc_dev); pData = (unsigned char *)CONFIG_FB_BASE; if (mmc){ if (mmc_init(mmc) == 0) { start = ALIGN(UBOOT_LOGO_BMP_ADDR, mmc->read_bl_len) / mmc->read_bl_len; count = ALIGN(size, mmc->read_bl_len) / mmc->read_bl_len; mmc->block_dev.block_read(&mmc->block_dev, start, count, pData); #ifdef CONFIG_ADV_UBOOT_LOGO_DEBUG printf("start %x \n" ,start); printf("mmc->read_bl_len %x \n" ,mmc->read_bl_len); printf("count %x \n" ,count); #endif bmpReady = 1; // for(i=0;i<count;i++) // printf("0x%x ",pData[i]); // printf("\n"); #ifdef CONFIG_ADV_UBOOT_LOGO_DEBUG printf("Display emmc logo !!! \n"); printf("DISPLAY_BPP %d !!! \n",DISPLAY_BPP); #endif } } //printf("display r g b !!! \n"); //bmpReady = 0; //r g b bpp is 16,is ok if (bmpReady == 0) { // Fill RGB frame buffer // Red for (i = 0; i < (DISPLAY_WIDTH * DISPLAY_HEIGHT * (DISPLAY_BPP / 8) / 3); i += (DISPLAY_BPP / 8)) { #if (DISPLAY_BPP == 16) pData[i + 0] = 0x00; pData[i + 1] = 0xF8; #else pData[i + 0] = 0x00; pData[i + 1] = 0x00; pData[i + 2] = 0xFF; #endif } // Green for (; i < (DISPLAY_WIDTH * DISPLAY_HEIGHT * (DISPLAY_BPP / 8) / 3) * 2; i += (DISPLAY_BPP / 8)) { #if (DISPLAY_BPP == 16) pData[i + 0] = 0xE0; pData[i + 1] = 0x07; #else pData[i + 0] = 0x00; pData[i + 1] = 0xFF; pData[i + 2] = 0x00; #endif } // Blue for (; i < DISPLAY_WIDTH * DISPLAY_HEIGHT * (DISPLAY_BPP / 8); i += (DISPLAY_BPP / 8)) { #if (DISPLAY_BPP == 16) pData[i + 0] = 0x1F; pData[i + 1] = 0x00; #else pData[i + 0] = 0xFF; pData[i + 1] = 0x00; pData[i + 2] = 0x00; #endif } } #endif //#ifdef CONFIG_ADV_UBOOT_LOGO_EMMC #else video_console_address = video_fb_address; #endif

- 4. Modify the red string part in the uboot-imx6/include/configs/mx6advantech_common.h file

@@ -51,6 +51,10 @@ #define CONFIG_PHYLIB #define CONFIG_PHY_ATHEROS #define CONFIG_ADV_UBOOT_LOGO #define CONFIG_ADV_UBOOT_LOGO_EMMC /* #define CONFIG_ADV_UBOOT_LOGO_DEBUG */ /* Command definition */ #define CONFIG_CMD_BMODE @@ -409,6 +413,33 @@ #define CONFIG_SYS_I2C_MXC_I2C3 /* enable I2C bus 3 */ #define CONFIG_SYS_I2C_SPEED 100000 #ifdef CONFIG_ADV_UBOOT_LOGO #ifdef CONFIG_ADVANTECH /* Framebuffer */ #define CONFIG_VIDEO #define CONFIG_VIDEO_IPUV3 #define CONFIG_CFB_CONSOLE #define CONFIG_VGA_AS_SINGLE_DEVICE #define CONFIG_SYS_CONSOLE_IS_IN_ENV #define CONFIG_SYS_CONSOLE_OVERWRITE_ROUTINE #define CONFIG_VIDEO_BMP_RLE8 #define CONFIG_SPLASH_SCREEN #define CONFIG_SPLASH_SCREEN_ALIGN #define CONFIG_BMP_16BPP #define CONFIG_VIDEO_LOGO #define CONFIG_VIDEO_BMP_LOGO #ifdef CONFIG_MX6DL #define CONFIG_IPUV3_CLK 198000000 #else #define CONFIG_IPUV3_CLK 264000000 #endif #define CONFIG_IMX_HDMI #define CONFIG_IMX_VIDEO_SKIP #endif /* #ifdef CONFIG_ADVANTECH */ #endif /* #ifdef CONFIG_ADV_UBOOT_LOGO */ #if defined(CONFIG_ANDROID_SUPPORT) #include "mx6sabreandroid_common.h" #else

- 5. You can download following file. Then put the decompressed files into the uboot-imx6/arch/arm/include/asm/ path

You can refer to Setting_up_SDK to setup environment for building u-boot image

After you patch file, you need to build u-boot image(Example:ROM-3420 DDR 1G)

- 1. Source environment(Example: Toolchain path:/opt/poky/2.1/)

source /opt/poky/2.1/environment-setup-cortexa9hf-neon-poky-linux-gnueabi

- 2. Build ROM-3420 1G u-boot image

make mx6qrom3420a1_1G_defconfig make -j4

Generate u-boot logo image

- For example: You can use picture editor tool(Photoshop) to generate a 800x480 u-boot logo image(16 bit BMP file)

- 1. U-boot logo file format

File name: adv_logo_800x480_16bit_rgb565.bmp Resolution: 800x480 Depth: 16 Bit BMP Advanced Modes: R5 G6 B5

- 2. Open original u-boot logo file by Photoshop tool

- 3. Save the new file

- 4. New file name:adv_logo_800x480_16bit_rgb565.bmp

- 5. Choose the type of file and press "OK" button to save the file

- Copy u-boot logo file(adv_uboot_logo.bmp) to linux OS(Example: Ubuntu), then produce a u-boot logo file that will actually be used

dd if=adv_logo_800x480_16bit_rgb565.bmp of=adv_logo_800x480_16bit_rgb565_new.bmp bs=1 skip=72 sync

- You can get a u-boot logo file by following link

Upload u-boot image and u-boot log image to eMMC by mgtool

- 1. Modify ucl2.xml file

<LIST name="ADV u-boot" desc="update u-boot"> <CMD state="BootStrap" type="boot" body="BootStrap" file ="firmware/u-boot.imx">Loading U-boot</CMD> <CMD state="BootStrap" type="load" file="firmware/zImage" address="0x12000000" loadSection="OTH" setSection="OTH" HasFlashHeader="FALSE">Loading Kernel.</CMD> <CMD state="BootStrap" type="load" file="firmware/fsl-image-mfgtool-initramfs-imx_mfgtools.cpio.gz.u-boot" address="0x12C00000" loadSection="OTH" setSection="OTH" HasFlashHeader="FALSE">Loading Initramfs.</CMD> <CMD state="BootStrap" type="load" file="firmware/zImage-%dtb%.dtb" address="0x18000000" loadSection="OTH" setSection="OTH" HasFlashHeader="FALSE">Loading device tree.</CMD> <CMD state="BootStrap" type="jump" > Jumping to OS image.</CMD> <CMD state="Updater" type="push" body="send" file="files/u-boot_crc.bin.crc">Sending u-boot.bin.crc</CMD> <CMD state="Updater" type="push" body="$ dd if=$FILE of=/dev/mmcblk%mmc% bs=512 seek=2">write u-boot.bin.crc</CMD> <CMD state="Updater" type="push" body="send" file="files/u-boot_crc.bin">Sending u-boot.bin</CMD> <CMD state="Updater" type="push" body="$ dd if=$FILE of=/dev/mmcblk%mmc% bs=512 seek=3">write u-boot.bin</CMD> <CMD state="Updater" type="push" body="send" file="files/adv_logo_800x480_16bit_rgb565_new.bmp" ifdev="MX6Q">Sending u-boot logo</CMD> <CMD state="Updater" type="push" body="$ dd if=$FILE of=/dev/mmcblk%mmc% bs=512 seek=2048 conv=fsync">write u-boot logo</CMD> <CMD state="Updater" type="push" body="$ echo Update Complete!">Done</CMD> </LIST>

- 2. Modify cfg.ini file

[LIST] name = ADV u-boot

- 3. Copy "u-boot_crc.bin.crc", "u-boot_crc.bin" and "adv_logo_800x480_16bit_rgb565_new.bmp" files to "3420A1LIVXXX_1G_mfgtools\Profiles\Linux\OS Firmware\files" folder

- 4. Finally, you can refer to Mfgtool to update u-boot image and u-boot logo image

LTIB

The following operations demonstrate how to customize one 800*480 boot logo for ROM-3420 with imx6LBV2210.

- get one 800*480 8bpp BMP ready, or convert from PPM to BMP file

- $ ppmtobmp -bpp=8 uboot_logo.ppm > uboot_logo.bmp

- convert to C file

- $ xxd -i uboot_logo.bmp > uboot_logo.c

- create new u-boot-2009.08/board/freescale/common/adv_bmp_reversed_800x480.c

unsigned char adv_bmp_reversed_800x480[] = {

//hexvalue copyed from uboot_logo.c

//...

//...

}

unsigned int adv_bmp_reversed_800x480_size = sizeof(adv_bmp_reversed_800x480);

- u-boot-2009.08/board/freescale/common/Makefile

#COBJS-${CONFIG_VIDEO_MX5} += fsl_bmp_600x400.o fsl_bmp_reversed_600x400.o

COBJS-${CONFIG_ADVANTECH} += adv_bmp_reversed_800x480.o

- Check the ADV loader version. For example: The ADV loader version is V2.210 in the following message

Adv-Boot 2009.08-advantech_rom3420_1G_V2.210_svn414 (Mar 14 2014 - 09:51:19)

- u-boot-2009.08/board/freescale/mx6q_rom-3420/mx6q_rom-3420.c

- 1. If ADV loader version of the device is less than the V.2350 version, modify the content as follows:

//extern unsigned char fsl_bmp_reversed_600x400[];

//extern int fsl_bmp_reversed_600x400_size;

extern unsigned char adv_bmp_reversed_800x480[];

extern int adv_bmp_reversed_800x480_size;

#if defined CONFIG_ADVANTECH

// AUO 7.0 inch color TFT LCD module G070VW01 V0

"WVGA", 60, 800, 480, 33898, 96, 24, 3, 10, 72, 7,

FB_SYNC_EXT,

FB_VMODE_NONINTERLACED,

FB_MODE_IS_DETAILED,

#else

"XGA", 60, 1024, 768, 15385, 220, 40, 21, 7, 60, 10,

FB_SYNC_EXT,

FB_VMODE_NONINTERLACED,

0,

#endif

#ifdef CONFIG_ADVANTECH

s = getenv("uboot_splashimage");

#else

s = getenv("splashimage");

#endif

if (NULL == s) {

puts("env splashimage not found!\n");

#ifdef CONFIG_ADVANTECH

puts("uboot_splashimage!\n");

#else

puts("env splashimage not found!\n");

#endif

return -1;

#ifdef CONFIG_ADVANTECH

// The di_clk_val is set according to LVDS display panel? spec.

// It also needs to comply with the pixelclock in fb_videomode structure.

// pixclock=(10^12)/clk_freq

ret = ipuv3_fb_init(&lvds_xga, di, IPU_PIX_FMT_RGB666,

DI_PCLK_LDB, 29500000);

#else

ret = ipuv3_fb_init(&lvds_xga, di, IPU_PIX_FMT_RGB666,

DI_PCLK_LDB, 65000000);

#endif

char *s;

ulong addr;

#ifdef CONFIG_ADVANTECH

s = getenv("uboot_splashimage");

#else

s = getenv("splashimage");

#endif

if (s != NULL) {

addr = simple_strtoul(s, NULL, 16);

- 2. If ADV loader version of the device is larger than the V.2350 version, modify the content as follows:

//extern unsigned char fsl_bmp_reversed_600x400[];

//extern int fsl_bmp_reversed_600x400_size;

extern unsigned char adv_bmp_reversed_800x480[];

extern int adv_bmp_reversed_800x480_size;

#if defined CONFIG_ADVANTECH

// AUO 7.0 inch color TFT LCD module G070VW01 V0

"WVGA", 60, 800, 480, 33898, 96, 24, 3, 10, 72, 7,

FB_SYNC_EXT,

FB_VMODE_NONINTERLACED,

FB_MODE_IS_DETAILED,

#else

"XGA", 60, 1024, 768, 15385, 220, 40, 21, 7, 60, 10,

FB_SYNC_EXT,

FB_VMODE_NONINTERLACED,

0,

#endif

#ifdef CONFIG_ADVANTECH

// The di_clk_val is set according to LVDS display panel? spec.

// It also needs to comply with the pixelclock in fb_videomode structure.

// pixclock=(10^12)/clk_freq

ret = ipuv3_fb_init(&lvds_xga, di, IPU_PIX_FMT_RGB666,

DI_PCLK_LDB, 29500000);

#else

ret = ipuv3_fb_init(&lvds_xga, di, IPU_PIX_FMT_RGB666,

DI_PCLK_LDB, 65000000);

#endif

- u-boot-2009.08/include/configs/mx6q_rom-3420_1G.h

#define CONFIG_SPLASH_SCREEN

- u-boot parameter

- 1. If ADV loader version of the device is less than the V.2350 version, modify the content as follows:

setenv bootargs_base 'setenv bootargs console=ttymxc0,115200 enable_wait_mode=off video_mode=extension pcie_testmode=off video=mxcfb0:dev=ldb,800x480M@60,if=RGB24 video=mxcfb1:off video=mxcfb2:off'

setenv uboot_splashimage '0x30000000'

setenv splashpos '0,0'

setenv lvds_num 0

saveenv

-

- 2. If ADV loader version of the device is larger than the V.2350 version, modify the content as follows:

setenv bootargs_base 'setenv bootargs console=ttymxc0,115200 enable_wait_mode=off video_mode=extension pcie_testmode=off video=mxcfb0:dev=ldb,800x480M@60,if=RGB24 video=mxcfb1:off video=mxcfb2:off'

setenv splashimage '0x30000000'

setenv splashpos '0,0'

setenv lvds_num 0

saveenv

Android

The following operations demonstrate how to customize one 1024*768 boot logo for RSB-4410 with 4410ABV1080.

- get one 1024*768 8bpp BMP ready, or convert from PPM to BMP file

- $ ppmtobmp -bpp=8 uboot_logo.ppm > uboot_logo.bmp

- convert to C file

- $ xxd -i uboot_logo.bmp > uboot_logo.c

- create new android/bootable/bootloader/uboot-imx/board/freescale/common/adv_bmp_reversed_1024x768.c

unsigned char adv_bmp_reversed_1024x768[] = {

//hexvalue copyed from uboot_logo.c

//...

//...

}

unsigned int adv_bmp_reversed_1024x768_size = sizeof(adv_bmp_reversed_1024x768);

- android/bootable/bootloader/uboot-imx/board/freescale/common/Makefile

#COBJS-${CONFIG_ADVANTECH} += adv_bmp_reversed_800x235.o

COBJS-${CONFIG_ADVANTECH} += adv_bmp_reversed_1024x768.o

- android/bootable/bootloader/uboot-imx/board/freescale/mx6q_rsb-4410/mx6q_rsb-4410.c

//extern unsigned char adv_bmp_reversed_800x235[];

//extern int adv_bmp_reversed_800x235_size;

extern unsigned char adv_bmp_reversed_1024x768[];

extern int adv_bmp_reversed_1024x768_size;

#if defined CONFIG_ADVANTECH

// AUO 7.0 inch color TFT LCD module G070VW01 V0

//"WVGA", 60, 800, 480, 33898, 96, 24, 3, 10, 72, 7,

//FB_SYNC_EXT,

//FB_VMODE_NONINTERLACED,

//FB_MODE_IS_DETAILED,

//Customer 1024x768 panel

"TCG121XGLPAPNN", 60, 1024, 768, 14202, 150, 150 , 20, 15 , 15, 8,

FB_SYNC_EXT,

FB_VMODE_NONINTERLACED,

FB_MODE_IS_DETAILED,

#else

#ifdef CONFIG_ADVANTECH

// The di_clk_val is set according to LVDS display panel spec.

// It also needs to comply with the pixelclock in fb_videomode structure.

// pixclock=(10^12)/clk_freq

//ret = ipuv3_fb_init(&lvds_xga, di, IPU_PIX_FMT_RGB666, DI_PCLK_LDB, 29500000);

ret = ipuv3_fb_init(&lvds_xga, di, IPU_PIX_FMT_RGB666, DI_PCLK_LDB, 70412617);

#else

if defined(CONFIG_ADVANTECH)

//addr = ioremap_nocache(iomem_to_phys(addr), adv_bmp_reversed_800x235_size);

addr = ioremap_nocache(iomem_to_phys(addr), adv_bmp_reversed_1024x768_size);

#else

#if defined(CONFIG_ADVANTECH)

//memcpy((char *)addr, (char *)adv_bmp_reversed_800x235, adv_bmp_reversed_800x235_size);

memcpy((char *)addr, (char *)adv_bmp_reversed_1024x768, adv_bmp_reversed_1024x768_size);

#else

- android/bootable/bootloader/uboot-imx/include/configs/mx6q_rsb-4410_1G.h

#define CONFIG_SPLASH_SCREEN

- android/bootable/bootloader/uboot-imx/include/configs/mx6q_rsb-4410_1G_android.h

//"lvds_num=1\0"

"lvds_num=0\0"

- u-boot parameter

| setenv bootargs 'console=ttymxc0,115200 androidboot.console=ttymxc0 vmalloc=400M init=/init video_mode=extension video=mxcfb0:dev=ldb,1024x768@60,bpp=32,if=RGB666 video=mxcfb1:off video=mxcfb2:off video=mxcfb3:off fbmem=10M androidboot.hardware=freescale pcie_testmode=off' |

How to customize Android logo

The following operations demonstrate how to customize one Android logo for RSB-4410 with 4410ABV1080.

- replace android/frameworks/base/core/res/assets/images/android-logo-mask.png with the new 24bpp PNG file

How to modify dts file for setting different framebuffer

Example: Because there is one ipu in i.MX6 SOLO,we set LVDS and HDMI as our default display.

If we want to change HDMI and VGA as our default display ,we have to modify and re-compile dts file.

imx6dl-rom5420-b1.dts default as below:

&lcd {

pinctrl-0 = <&pinctrl_ipu1_4>;

status = "disabled"

};

&ldb {

lvds-channel@0 {

crtc = "ipu1-di0";

};

lvds-channel@1 {

status ="disabled";

};

};

&mxcfb3 {

status = "okay";

};

mxcfb3 is mapped to lvds (you can check imx6qdl-advantech.dtsi)

We want to change to HDMI+VGA

&lcd {

pinctrl-0 = <&pinctrl_ipu1_4>;

status = "okay";

};

&ldb {

status ="disabled";

};

&mxcfb2 {

mode_str ="1366x768M@60";

status = "okay";

};

Then re-compile dts file and replace

How to bring up panel in Yocto 2.5 and later

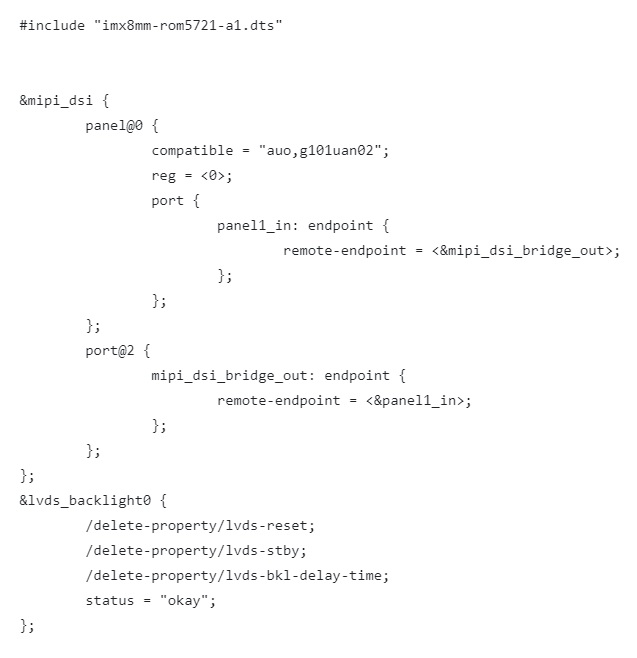

- Yocto 2.5

- mipi dsi

-

-

- Refer to adv-imx8mm-rom5721-a1-auog101uan02.dts

-

&mipi_dsi {

panel@0 {

compatible = "auo,g101uan02";

reg = <0>;

port {

panel1_in: endpoint {

remote-endpoint = <&mipi_dsi_bridge_out>;

};

};

};

port@2 {

mipi_dsi_bridge_out: endpoint {

remote-endpoint = <&panel1_in>;

};

};

};

-

-

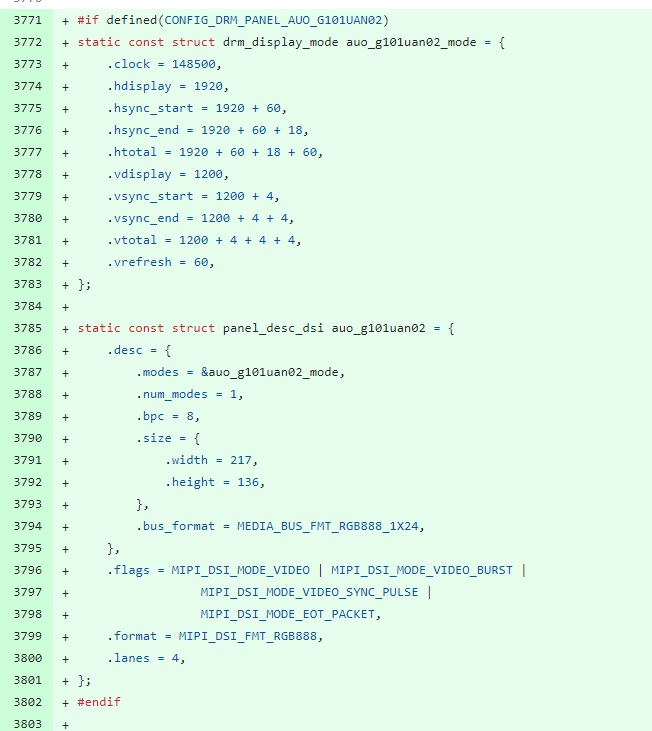

- Then refer to drivers/gpu/drm/panel/panel-simple.c

-

#if defined(CONFIG_DRM_PANEL_AUO_G101UAN02)

static const struct drm_display_mode auo_g101uan02_mode = {

.clock = 148500,

.hdisplay = 1920,

.hsync_start = 1920 + 60,

.hsync_end = 1920 + 60 + 18,

.htotal = 1920 + 60 + 18 + 60,

.vdisplay = 1200,

.vsync_start = 1200 + 4,

.vsync_end = 1200 + 4 + 4,

.vtotal = 1200 + 4 + 4 + 4,

.vrefresh = 60,

};

static const struct panel_desc_dsi auo_g101uan02 = {

.desc = {

.modes = &auo_g101uan02_mode,

.num_modes = 1,

.bpc = 8,

.size = {

.width = 217,

.height = 136,

},

},

.flags = MIPI_DSI_MODE_VIDEO |

MIPI_DSI_MODE_VIDEO_BURST |

MIPI_DSI_CLOCK_NON_CONTINUOUS,

.format = MIPI_DSI_FMT_RGB888,

.lanes = 4,

};

#endif

#if defined(CONFIG_DRM_PANEL_AUO_G101UAN02)

.compatible = "auo,g101uan02",

.data = &auo_g101uan02

}, {

#endif

- mipi dsi to lvds bridge

-

-

- Refer to adv-imx8mm-rom5721-a1.dts

- Fill initial value by panel into panel-init-sequence

-

&mipi_dsi {

status = "okay";

panel@0 {

compatible = "toshiba,tc358775";

reg = <0>;

dsi,flags = <(MIPI_DSI_MODE_VIDEO | MIPI_DSI_MODE_VIDEO_BURST | MIPI_DSI_MODE_LPM | MIPI_DSI_MODE_EOT_PACKET)>;

dsi,format = <MIPI_DSI_FMT_RGB888>;

dsi,lanes = <4>;

bus-format = <0x100a>;

bus-flags = <10>;

panel-init-sequence = [

29 00 06 3C 01 03 00 02 00

29 00 06 14 01 02 00 00 00

29 00 06 64 01 00 00 00 00

29 00 06 68 01 00 00 00 00

29 00 06 6C 01 00 00 00 00

29 00 06 70 01 00 00 00 00

29 00 06 34 01 1F 00 00 00

29 00 06 10 02 1F 00 00 00

29 00 06 04 01 01 00 00 00

29 00 06 04 02 01 00 00 00

29 00 06 50 04 20 01 F0 03

29 00 06 54 04 06 00 32 00

29 00 06 58 04 20 03 C8 00

29 00 06 5C 04 04 00 04 00

29 00 06 60 04 E0 01 14 00

29 00 06 64 04 01 00 00 00

29 01 06 A0 04 2D 80 44 00

29 00 06 A0 04 2D 80 04 00

29 00 06 04 05 04 00 00 00

29 00 06 80 04 00 01 02 03

29 00 06 84 04 04 07 05 08

29 00 06 88 04 09 0A 0E 0F

29 00 06 8C 04 0B 0C 0D 10

29 00 06 90 04 16 17 11 12

29 00 06 94 04 13 14 15 1B

29 14 06 98 04 18 19 1A 06

29 78 06 9C 04 31 00 00 00

];

display-timings {

native-mode = <&timing0>;

timing0: timing0 {

clock-frequency = <33300000>;

hactive = <800>;

vactive = <480>;

hback-porch = <50>;

hfront-porch = <200>;

vback-porch = <4>;

vfront-porch = <20>;

hsync-len = <6>;

vsync-len = <4>;

hsync-active = <0>;

vsync-active = <0>;

de-active = <0>;

pixelclk-active = <0>;

};

};

};

};

-

-

- Then refer to drivers/gpu/drm/panel/panel-simple.c

-

#ifdef CONFIG_ARCH_ADVANTECH

.compatible = "toshiba,tc358775",

.data = NULL

}

#endif

- Yocto 3.0

- mipi dsi

-

-

- Refer to imx8mm-rom5721-a1-auog101uan02.dts

-

&mipi_dsi {

panel@0 {

compatible = "auo,g101uan02";

reg = <0>;

port {

panel1_in: endpoint {

remote-endpoint = <&mipi_dsi_bridge_out>;

};

};

};

port@2 {

mipi_dsi_bridge_out: endpoint {

remote-endpoint = <&panel1_in>;

};

};

};

-

-

- Then refer to drivers/gpu/drm/panel/panel-simple.c

-

#if defined(CONFIG_DRM_PANEL_AUO_G101UAN02)

static const struct drm_display_mode auo_g101uan02_mode = {

.clock = 148500,

.hdisplay = 1920,

.hsync_start = 1920 + 60,

.hsync_end = 1920 + 60 + 18,

.htotal = 1920 + 60 + 18 + 60,

.vdisplay = 1200,

.vsync_start = 1200 + 4,

.vsync_end = 1200 + 4 + 4,

.vtotal = 1200 + 4 + 4 + 4,

.vrefresh = 60,

};

static const struct panel_desc_dsi auo_g101uan02 = {

.desc = {

.modes = &auo_g101uan02_mode,

.num_modes = 1,

.bpc = 8,

.size = {

.width = 217,

.height = 136,

},

.bus_format = MEDIA_BUS_FMT_RGB888_1X24,

},

.flags = MIPI_DSI_MODE_VIDEO | MIPI_DSI_MODE_VIDEO_BURST |

MIPI_DSI_MODE_VIDEO_SYNC_PULSE |

MIPI_DSI_MODE_EOT_PACKET,

.format = MIPI_DSI_FMT_RGB888,

.lanes = 4,

};

#endif

#if defined(CONFIG_DRM_PANEL_AUO_G101UAN02)

.compatible = "auo,g101uan02",

.data = &auo_g101uan02

}, {

#endif

- mipi dsi to lvds bridge

-

-

- Refer to imx8mm-rom5721-a1.dts

- Fill initial value by panel into panel-init-sequence

-

&mipi_dsi {

status = "okay";

panel@0 {

compatible = "auo,g070vw01v0";

reg = <0>;

backlight=<&lvds_backlight0>;

panel-init-sequence = [

29 00 06 3C 01 03 00 02 00

29 00 06 14 01 02 00 00 00

29 00 06 64 01 00 00 00 00

29 00 06 68 01 00 00 00 00

29 00 06 6C 01 00 00 00 00

29 00 06 70 01 00 00 00 00

29 00 06 34 01 1F 00 00 00

29 00 06 10 02 1F 00 00 00

29 00 06 04 01 01 00 00 00

29 00 06 04 02 01 00 00 00

29 00 06 50 04 20 01 F0 03

29 00 06 54 04 06 00 32 00

29 00 06 58 04 20 03 C8 00

29 00 06 5C 04 04 00 04 00

29 00 06 60 04 E0 01 14 00

29 00 06 64 04 01 00 00 00

29 01 06 A0 04 2D 80 44 00

29 00 06 A0 04 2D 80 04 00

29 00 06 04 05 04 00 00 00

29 00 06 80 04 00 01 02 03

29 00 06 84 04 04 07 05 08

29 00 06 88 04 09 0A 0E 0F

29 00 06 8C 04 0B 0C 0D 10

29 00 06 90 04 16 17 11 12

29 00 06 94 04 13 14 15 1B

29 14 06 98 04 18 19 1A 06

29 78 06 9C 04 31 00 00 00

];

};

};

-

-

- Then refer to drivers/gpu/drm/panel/panel-simple.c

-

static const struct drm_display_mode auo_g070vw01v0_mode = {

.clock = 29500,

.hdisplay = 800,

.hsync_start = 800 + 24,

.hsync_end = 800 + 24 + 72,

.htotal = 800 + 24 + 72 + 96,

.vdisplay = 480,

.vsync_start = 480 + 10,

.vsync_end = 480 + 10 + 7,

.vtotal = 480 + 10 + 3 + 7,

.vrefresh = 60,

};

static const struct panel_desc_dsi auo_g070vw01v0 = {

.desc = {

.modes = &auo_g070vw01v0_mode,

.num_modes = 1,

.bpc = 8,

.size = {

.width = 170,

.height = 110,

},

.bus_format = MEDIA_BUS_FMT_RGB888_1X24,

},

.flags = MIPI_DSI_MODE_VIDEO | MIPI_DSI_MODE_VIDEO_BURST | MIPI_DSI_MODE_LPM | MIPI_DSI_MODE_EOT_PACKET,

.format = MIPI_DSI_FMT_RGB888,

.lanes = 4,

};

#if defined(CONFIG_ARCH_ADVANTECH)

.compatible = "auo,g070vw01v0",

.data = &auo_g070vw01v0

}

#endif

ThreeDisplayImx8

LVDS0+DSI+HDMI Three Display

Please intergate the imx8mp-rom5722-a1-adv7535.dts and imx8mp-rom5722-a1-lvds0-auo.dts.

Refer : The attachment file. (Three_display.7z)

http://ess-wiki.advantech.com.tw/view/File:Three_display.7z

Limitation

i.MX6 Dual Display Capilities

i.MX6 Q/D

- If you want to support two Full HD resloution , you have to allocate on two different ipu

i.MX6 Solo

- Solo cpu have only one ipu ,so only support the highest resolution are 1920X1080 ,1366X768

New Panel in 2021

G156HCE-L01

G156HCE-L01 is LVDS Dual Channel (2 ch 8-bit).

(1)clock-frequency --> Clock (MHz) => 141860000

(2)hactive --> Horizontal Active Display Period => 1920

(3)vactive --> Vertical Active Display Period => 1080

(4)hback-porch + hfront-porch + hsync-len (Total) = Blanking => 35+35+35=105

(5)vback-porch + vfront-porch + vsync-len (Total) = Blanking => 10+10+10=30

Yocto 2.1

Patch file based on Yocto 2.1 linux kernel [commit: c4291bf8354b19719ed67650d3d05f95d8caf9c5]

https://github.com/ADVANTECH-Corp/linux-imx6/commit/c4291bf8354b19719ed67650d3d05f95d8caf9c5

Patch File: 15 inch panel.patch

Uboot Command:

setenv mmcargs setenv bootargs console=${console},${baudrate} ${smp} root=${mmcroot} video=mxcfb0:dev=ldb,1920x1080M@60,if=RGB24 video=mxcfb1:off video=mxcfb2:off

G121XCE-L02

G121XCE-L02 is LVDS Single Channel (1 ch 6/8-bit).

(1)clock-frequency --> Clock (MHz) => 64900000

(2)hactive --> Horizontal Active Display Period => 1024

(3)vactive --> Vertical Active Display Period => 768

(4)hback-porch + hfront-porch + hsync-len (Total) = Blanking => 110+110+100=320

(5)vback-porch + vfront-porch + vsync-len (Total) = Blanking => 13+13+12=38

Yocto 2.1

Patch file based on Yocto 2.1 linux kernel [commit: c4291bf8354b19719ed67650d3d05f95d8caf9c5]

https://github.com/ADVANTECH-Corp/linux-imx6/commit/c4291bf8354b19719ed67650d3d05f95d8caf9c5

Patch File: 15 inch panel.patch

Uboot Command:

setenv mmcargs setenv bootargs console=${console},${baudrate} ${smp} root=${mmcroot} video=mxcfb0:dev=ldb,1024x768M@60,if=RGB24 video=mxcfb1:off video=mxcfb2:off

G104XCE-L01

G104XCE-L01 is LVDS Single Channel (1 ch 6/8-bit).

(1)clock-frequency --> Clock (MHz) => 65000000

(2)hactive --> Horizontal Active Display Period => 1024

(3)vactive --> Vertical Active Display Period => 768

(4)hback-porch + hfront-porch + hsync-len (Total) = Blanking => 110+110+100=320

(5)vback-porch + vfront-porch + vsync-len (Total) = Blanking => 13+13+12=38

Panel in iMX8

AUOG101UAN02

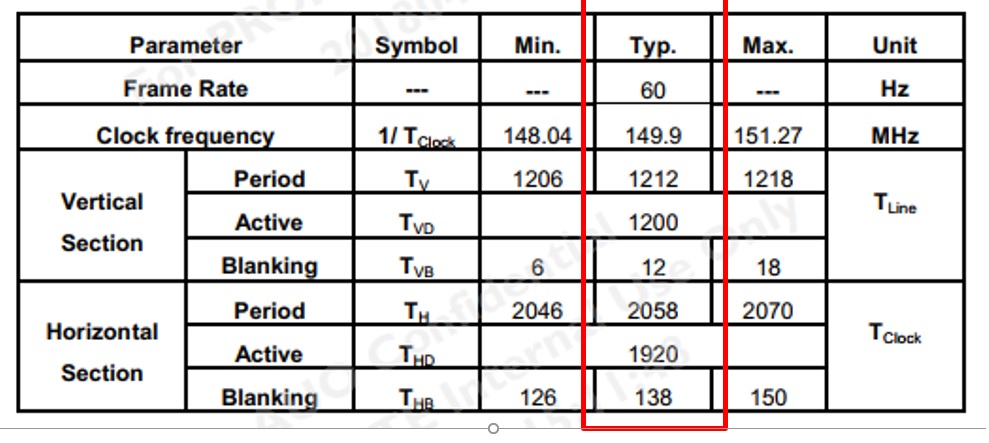

(1) ROM5721 iMX8MM AUO G101UAN02 10.1” MIPI Interface

(2) Pixel clock(MHz) => LCK Setting (h_active + hfp + hbp + h_sync) * (v_active + vfp + vbp + v_sync) * fps DSI clock(Mbps) ((h_active + hfp + hbp + h_sync) * (v_active + vfp + vbp + v_sync) * fps * bpp) / lane_number RGB888 bpp is 3X8=24bits

(3) Kernel driver CONFIG_DRM_PANEL_SIMPLE drivers/gpu/drm/panel/panel-simple.c https://github.com/ADVANTECH-Corp/linux-imx/commit/91081d143e0528d9920a284f640e80c3a8cb5385#diff-b0efb865b9590da1c62bb09d5b597a61bcc769888ce286b5c8a9f72d35fc3788

(4) DTS Setting --> Include the backlight enable in dts.

G070VW01

(1) In ROM5721 iMX8MM

(2) Kernel version 5.15.52

(3) Porting backlight and brightness levels setting Refer: https://github.com/ADVANTECH-Corp/linux-imx/blob/adv_5.15.52_2.1.0/arch/arm64/boot/dts/freescale/imx8mm-rom5721-a1.dts

The pwm setting follow dts example and setting brightness levels.

lvds_backlight0: lvds_backlight@0 {

compatible = "pwm-backlight";

pwms = <&pwm4 0 1000000 0>;

brightness-levels = < 0 1 2 3 4 5 6 7 8 9

10 11 12 13 14 15 16 17 18 19

20 21 22 23 24 25 26 27 28 29

30 31 32 33 34 35 36 37 38 39

40 41 42 43 44 45 46 47 48 49

50 51 52 53 54 55 56 57 58 59

60 61 62 63 64 65 66 67 68 69

70 71 72 73 74 75 76 77 78 79

80 81 82 83 84 85 86 87 88 89

90 91 92 93 94 95 96 97 98 99

100>;

default-brightness-level = <80>;

};

- ↑ Cite error: Invalid

<ref>tag; no text was provided for refs namedhttp:.2F.2Fadvdownload.advantech.com.2Fproductfile.2FDownloadfile1.2F1-Q18T9C.2FIDK-1105_USER_MANUAL_ED.1_FINAL.PDF - ↑ http://advdownload.advantech.com/productfile/Downloadfile1/1-Q18T9C/IDK-1105_USER_MANUAL_ED.1_FINAL.PDF